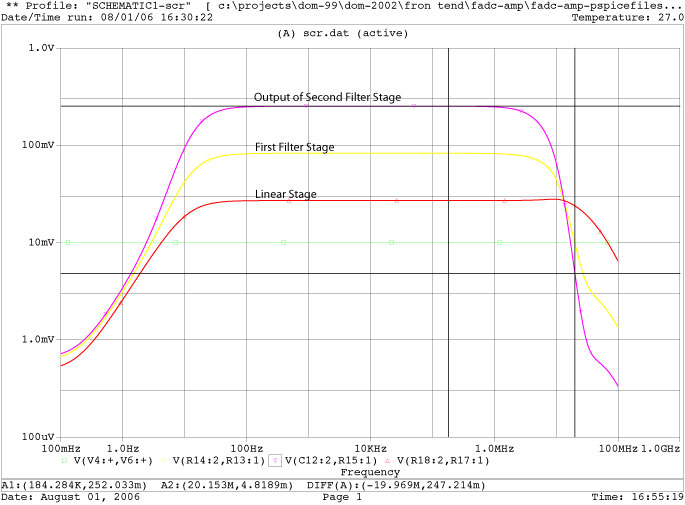

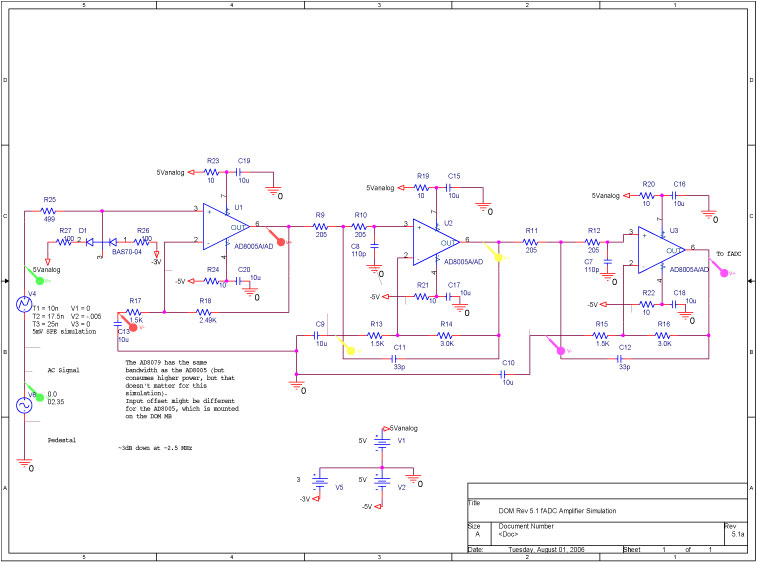

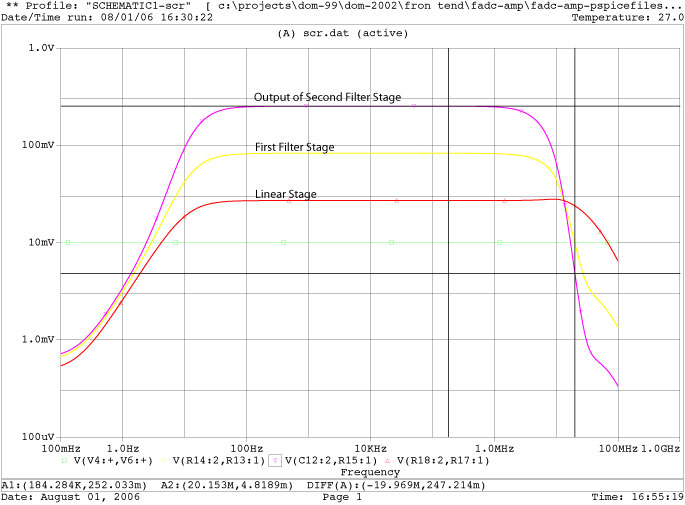

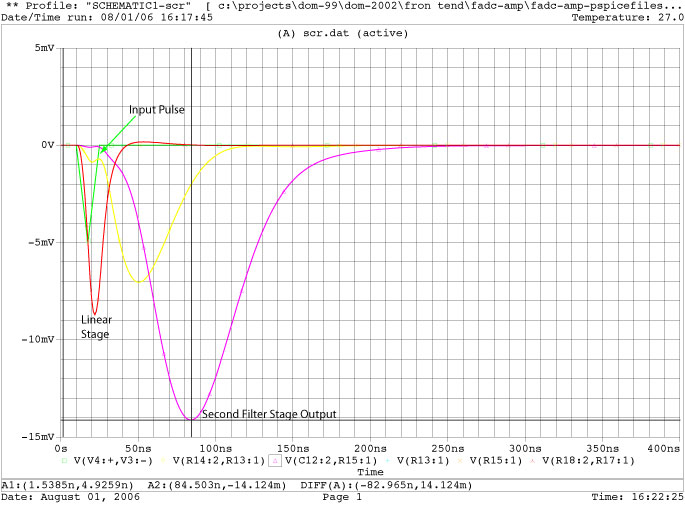

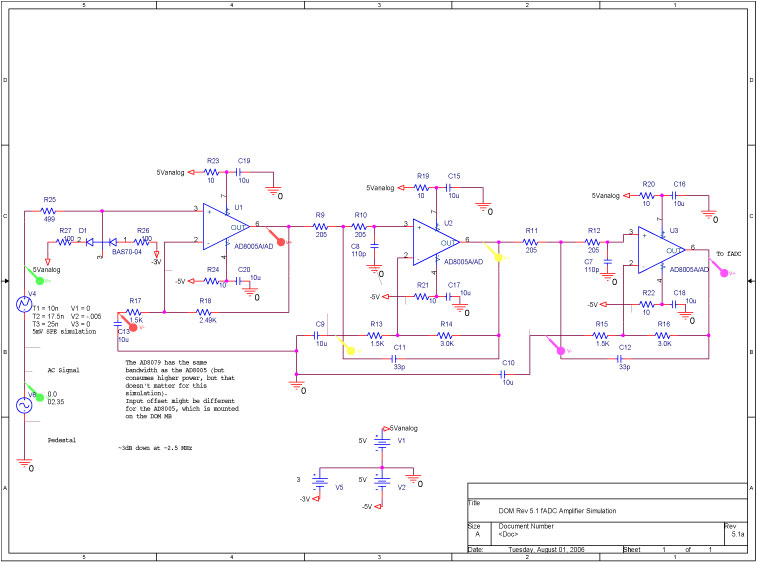

A band-width limited amplifies shapes the waveform sampled by the 40 MHz high speed, pipeline Analog to Digital Converter (fast ADC, or fADC). It is well known that the shaping time is twice the time constant (peaking time), per pole of the filter network. The time constant is (205 Ω x 110pF) = 22.5ns.

The amplifier-filter topology consists of an amplifier preceding two cascaded two-pole active filters. See the lower left corner of the front-end schematic.

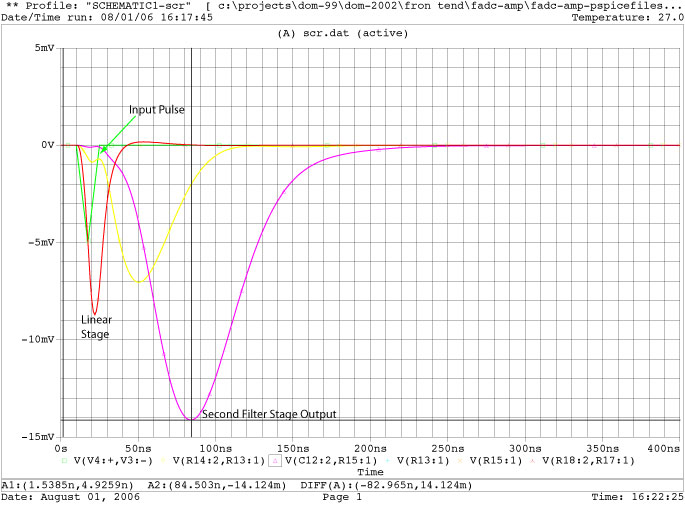

The response of the filter to an impulse (a pulse substantially like a photomultiplier pulse), yields a pulse that can be sampled at least twice on its rising, or falling edge by the fADC. This waveform easily satisfies the Nyquist–Shannon sampling theorem. (Negligeable signal energy at half the sampling frequency)

The gain is adjusted so that a 5 mV SPE (approximated by a triangular pulse 15ns wide at its base, 5mV high), produces a 12mV (six ADC count) pulse at the input of the fADC.

|

|

|