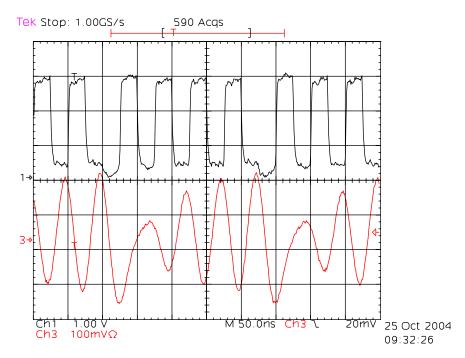

Ch1: Oscillator output pin Ch3: Filtered clk monitor test point.

Random phase changes disrupt the capacity of the PLLs in the EPXA4 to follow the clock.