DOM MB Diagnosis page

Board ID:

Rev V5.0L 000471

Source:

From STF testing crew

Symptoms:

Temperature related failures

of Local Coincidence Loopback

tests.

Analyst(s):

G. Przybylski

Analysis Procedure(s):

Operated board in forth monitor

executing lctestboth in a loop. The continuity between TB10 and

T3, or

between JP3-7 and TB10 could be influenced by torquing on TB10 with

tweezers. This implicates trace and via integrity. Removed

keystone solder post, and solder from PTH. Examined under microscope

for cracks in traces. Non faults were positively identified.

August 11; Board fell 3 feet to floor during handling.

Retest:

Install jumper wire from T3-4 to JP3-7 to cure Local Coincidence

loop-back test failure.

No boot failures during about 800 reboot cycles every 2 minutes, while

cycling temperature between -55°C and +65°C every

90 minutes.

With Rev 25 CPLD firmware, this board sometimes fails the boot test.

Low temperature, -45°C to -75°C,

profile - Results:

Many ADC 0 failures at and below -60°C.

ATWD A Ch1 baseline fail at -75°C

Local coincidence loop-back test fails at and below -70°C.

STF @ +65°C produces no failures.

Root cause:

Copper continuity problem.

This is the second case where this net is implicated in an LC failure.

This is the second continuity failure involving the same net... both

problems temperature dependent.

Mitigation:

The most agressive fault isolation

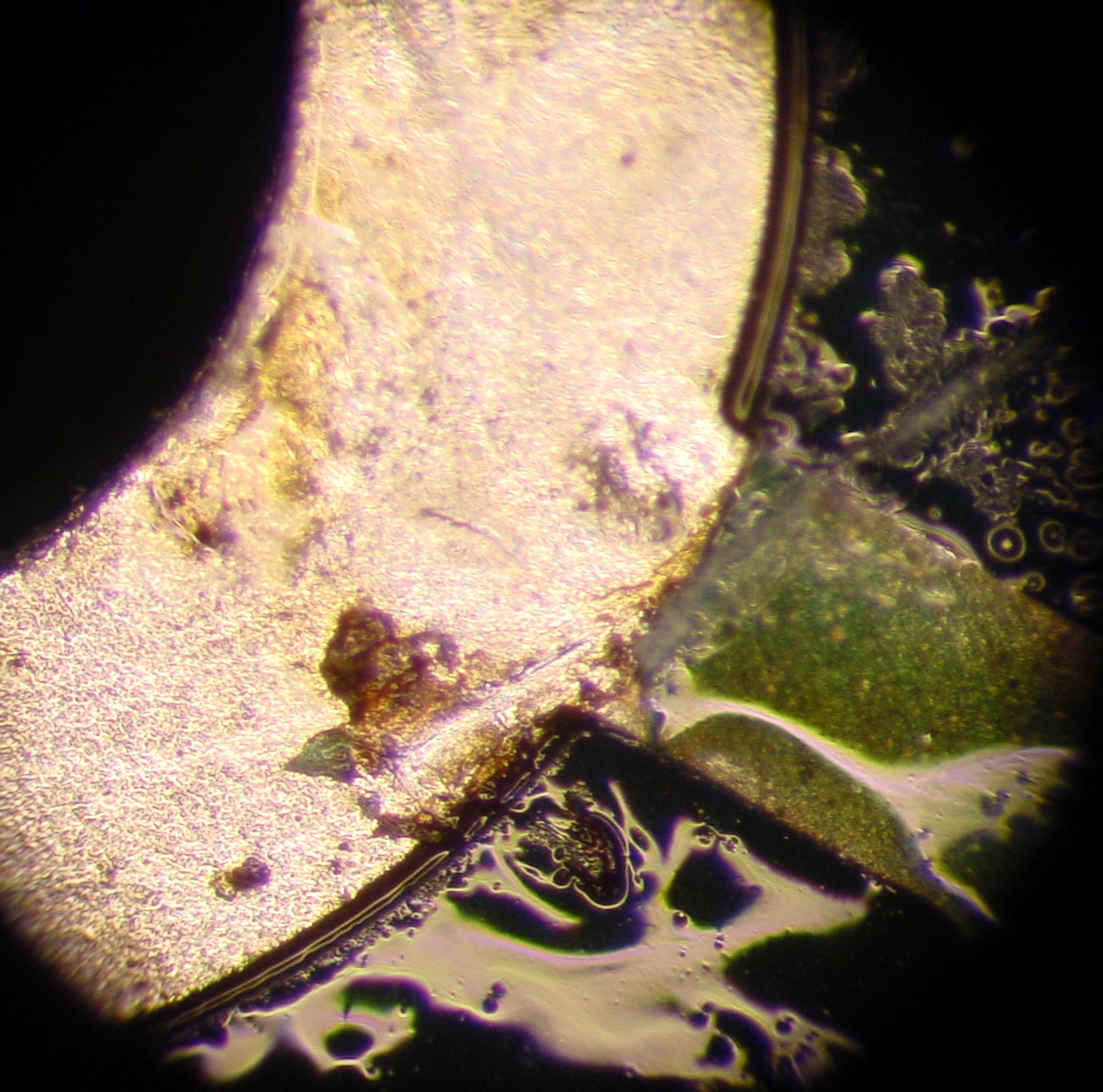

technique would be sectioning the board where the trace meets the via,

in order to allow the examination of the interfaces. So far

this option has not been taken. If additional failures are found,

it may be.

Disposition:

Not for Deployment due to Green Wire Repair.

Use for ATWD tester.

Any Other Information:

Traveler August 7

Traveler August 11

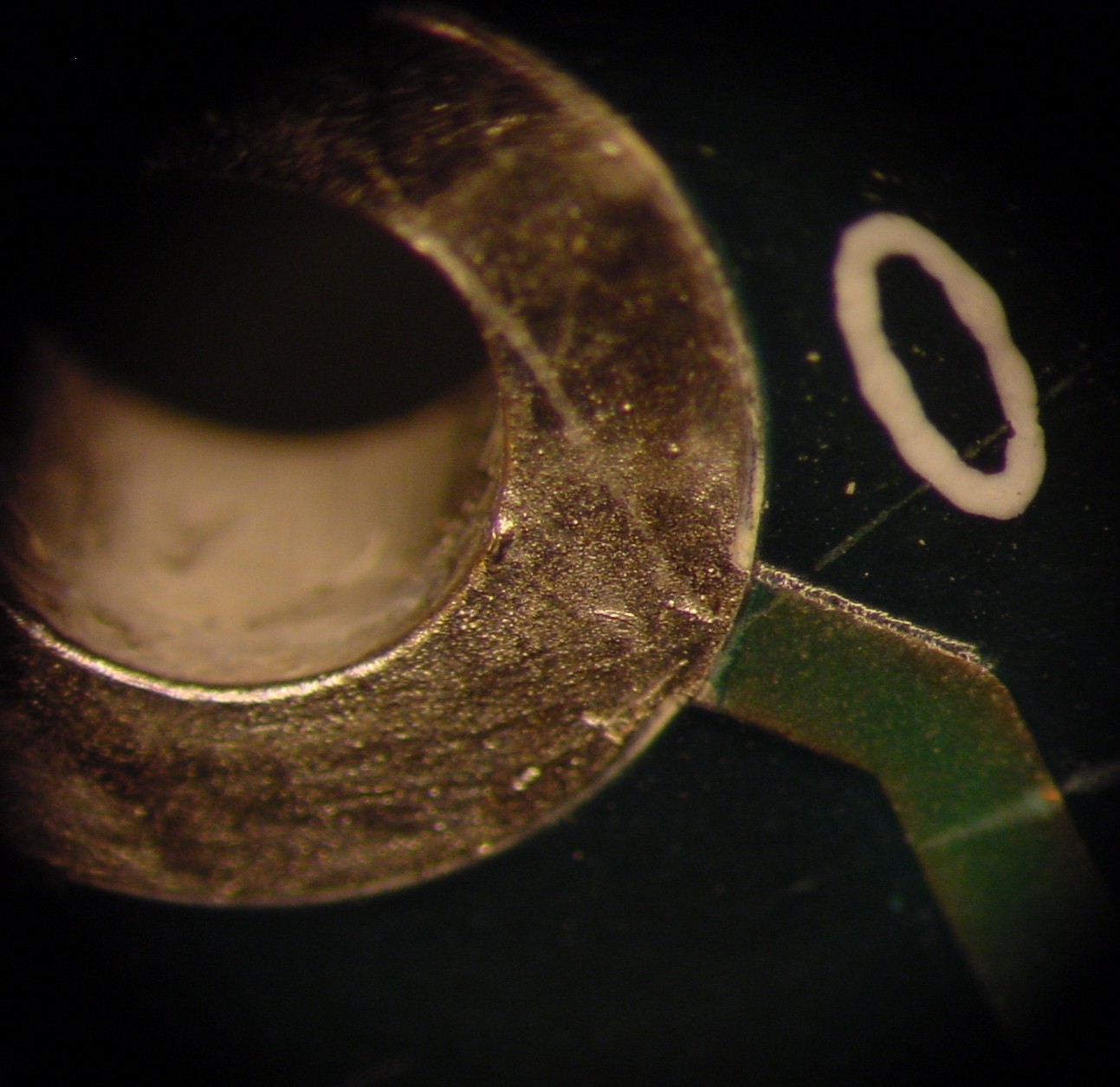

TB10 Via, Oblique view

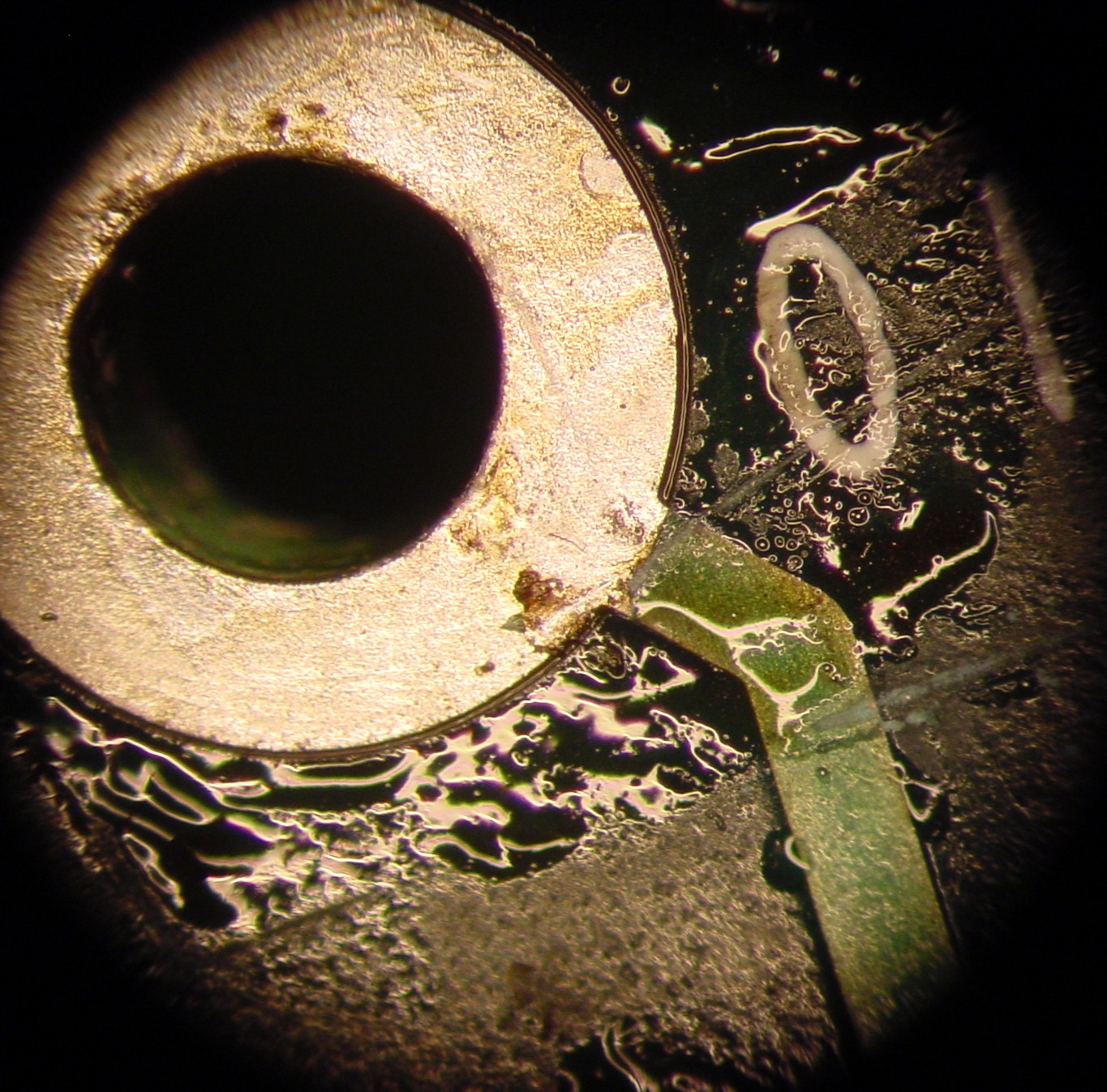

TB10 Via before flux clean-up.

There is no obvious separation between the via and the trace to the

lower right, but, before removal of the post, the net was intermittent

when torque was applied to the post with a pair of tweezers.

If there is a microcrack, then it is hidden, or filled with solder.

9/13/04 gtp