| 10 MHz GPS Output to lower LEMO

connector on DSB |

1Hz GPS Output to upper LEMO

connector on DSB |

Observed 1 Hz _↑‾ to 10 MHz _↑‾ timing (ns) |

| J5 |

J4 |

13.2 |

| J5 |

J6 |

26.1 (recommended) |

| J5 |

J8 |

13.4 |

| J7 |

J4 |

73.0 (recommended) |

| J7 |

J6 |

86.0 |

| J7 |

J8 |

73.2 |

| J9 |

J4 |

12.9 |

| J9 |

J6 |

26.0 |

| J9 |

J8 |

13.3 (recommended) |

| From |

To |

Behavior |

| 67ns |

95ns |

Trouble free |

| 8.0ns |

31ns |

Trouble free |

| 3ns |

4ns | Violation for DOR

Rev 0 |

| 5ns | 8ns |

Violation for DOR

Rev 1 |

| 10 MHz source |

1Hz source |

1 Hz _↑‾ to 10 MHz

_↑‾ timing (ns) |

| J5 |

J4 |

13.1 |

| J5 |

J9 | 13.3 |

| J6 |

J4 |

5.4

(Forbidden) |

| J6 |

J9 |

5.8

(Forbidden) |

| J7 |

J4 |

72.9 |

| J7 |

J9 |

73.2 |

| J8 |

J4 |

13.0 |

| J8 |

J9 |

13.2 |

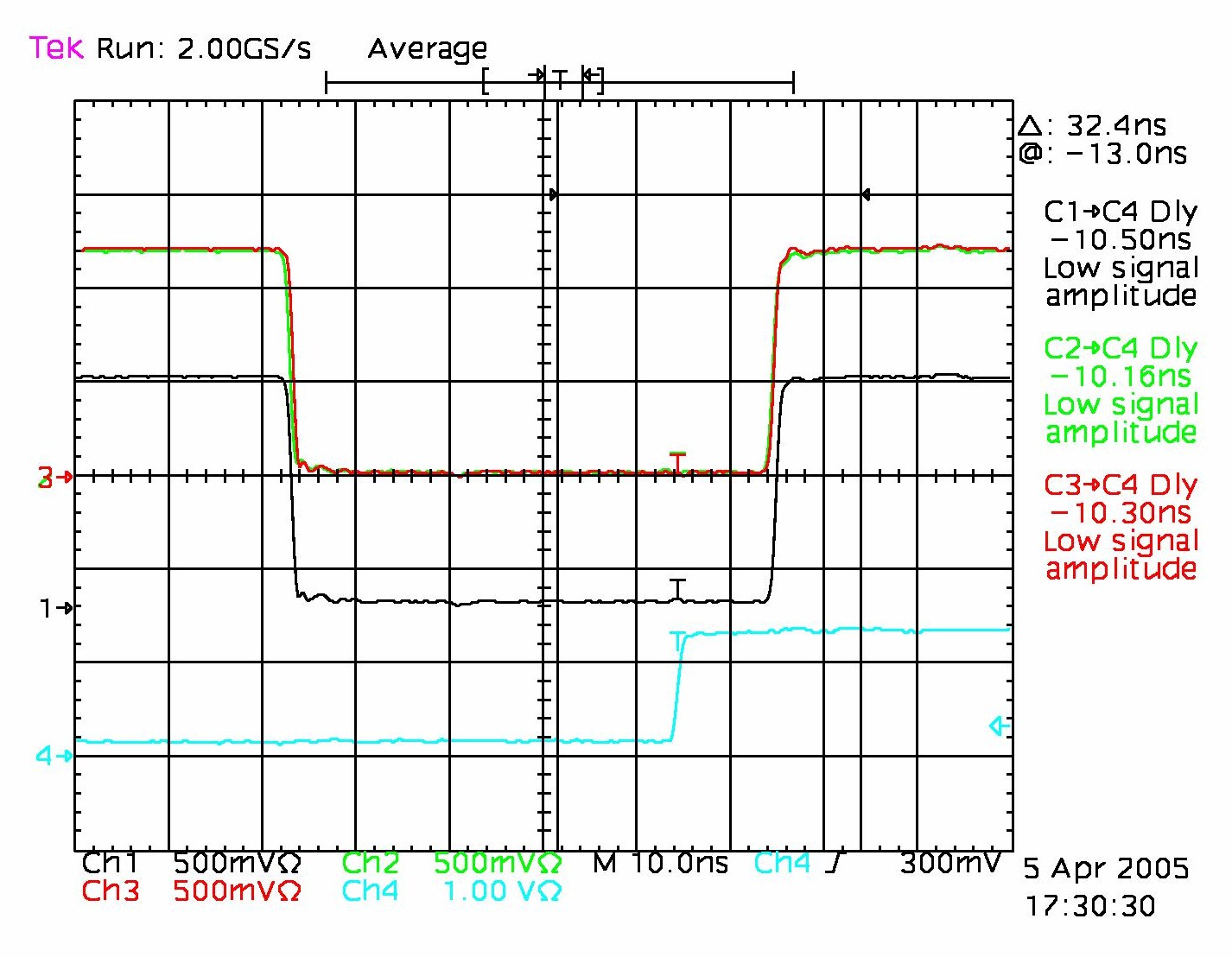

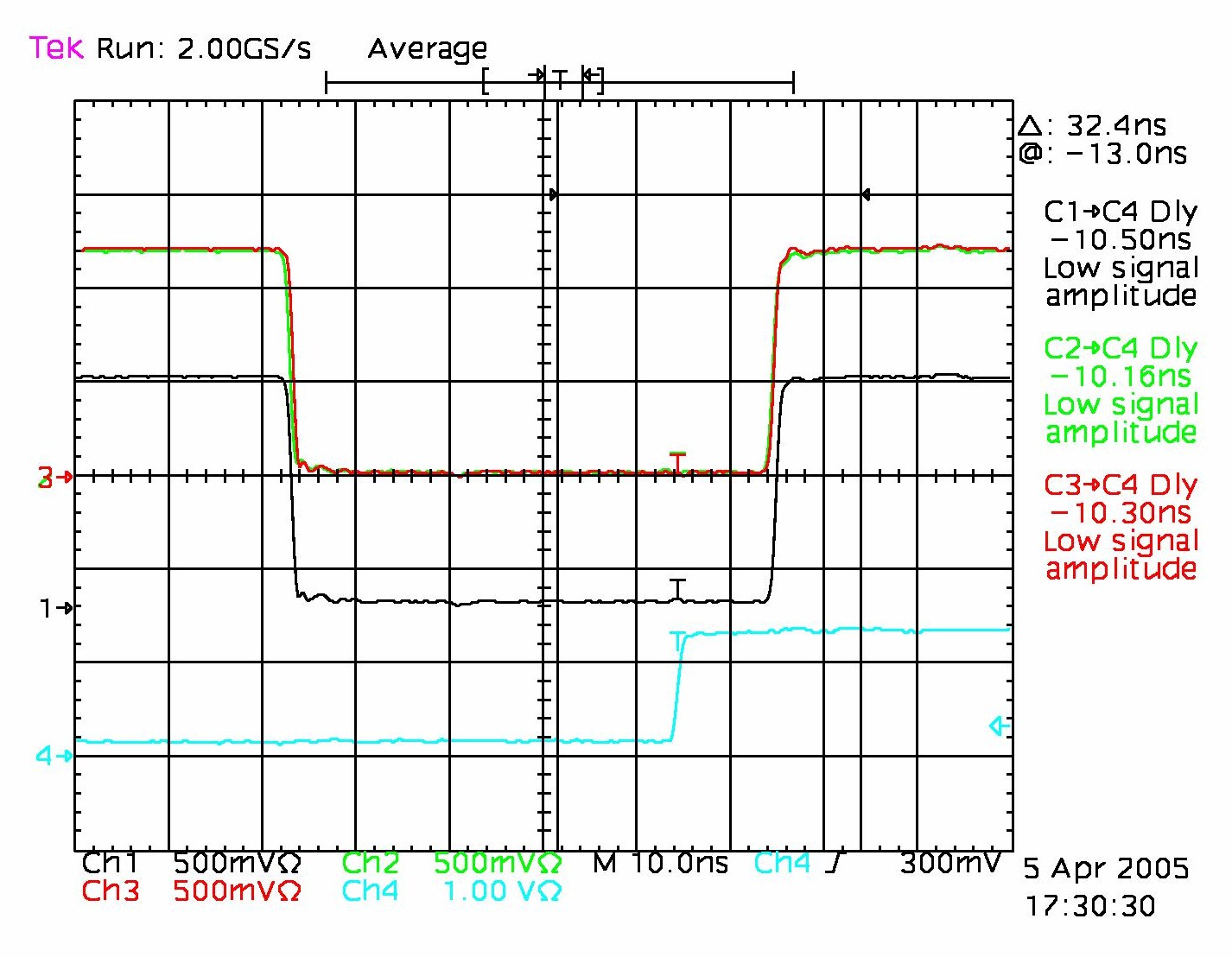

| 1Hz

to 10 MHz Clock Skew at DSB JP4 |

1Hz, 10 MHz, and 20MHz clock

skew in DOR |

|

|