| The breadboard circuit

matches to a 50 ohm 3V source (a typical GPS clock BNC output

characteristic), to a 100 ohm low level load. The

voltage division of the resistor network on the left yields

approximately 0.16V at the input to the transformer. The

transformer ratio turns that input voltage into approximately 90mV at

the twisted pair. The signal from this breadboard is coupled into

comparators in the DSB that drive the fan-out. The low input

level delivered by this matching unit is a relatively good

sensitivity test of the DSB comparator inputs. |

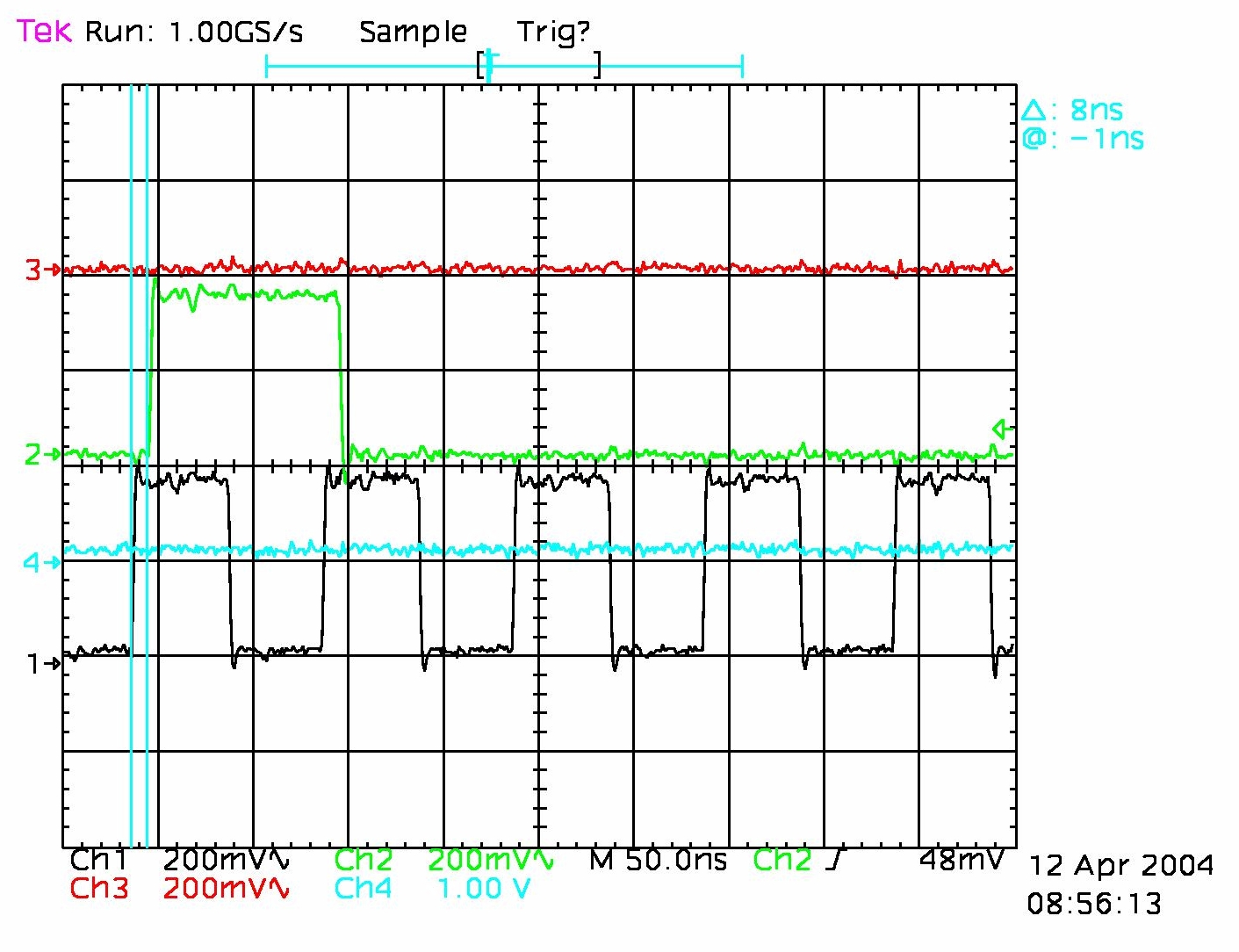

| The LVDS signals are

differential, so the breadboard circuit is designed terminate the 100

ohm characteristic impedance of the Cat-5 cable with resistors to a

common point, which floats up to the mid point of the differential

voltage. To monitor the outputs, plug into a scope with the

inputs set to 1M termination impedance, 100mV/div, and AC

coupling. |