The DOM PLD contains an encoder and decoder for these signals, so communications

with the DOM CPU is possible even before the FPGA is loaded. High

speed communications depends upon functionality in the DOM FPGA.

|

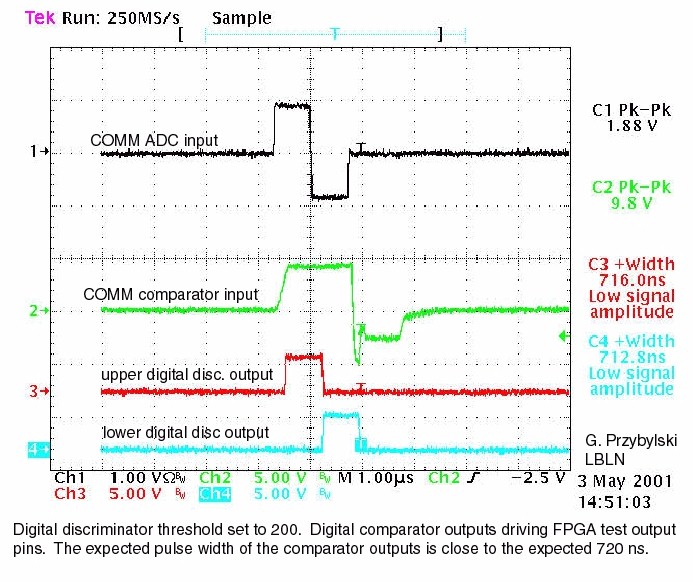

The data transmitter DAC couples its signal to the receiver

ADC and through a non-linear amplifier to an analog window comparator.

(The circuits were not designed for duplex operation) The level of

transmit ADC is sufficient to overdrive the shaping amplifier. The

flat topping of the green trace is indicative of saturation or clipping

in the amplifier stage. The stretching causes some problems decoding signals

at high speeds. The digital comparators see an undistorted signal. |

The communications waveforms must, of course, be converted back to digital

signals. The testboards and the DOMs contain hardware for two kinds

of signal acquisition. Two comparators create a window around the

baseline communications waveform. Positive and negative excursions outside

the window produce comparator outputs which must be properly decoded to

recover the information content. The typical

communications input can be compared with the transmitted output as

seen by the local communications

input.

< Previous Next

>