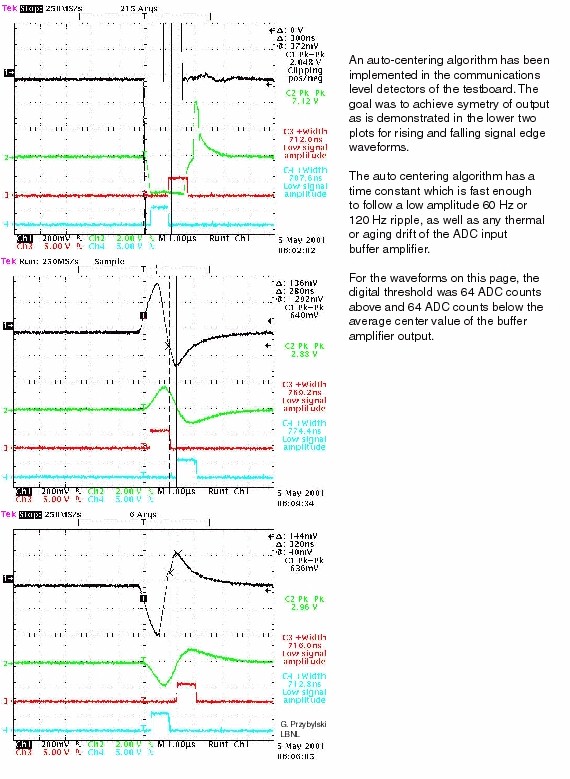

The above digital discriminator waveforms asymmetries suggest that

the digital comparator center doesn't match the baseline voltage delivered

to the ADC. The average finding function now implemented in the testboard

FPGA digital discriminator produces much better

balanced results.

The +/- 64 ADC count digital comparator thresholds result in a dead-band

for the comparators of approximately five clock pulses. The high

signal to noise ratio of the signal suggests a reduction of the threshold

is justified. When the threshold is reduced to +/- 32 counts,

dead-band drops to only one clock cycle.

< Previous Next

>

The +/- 64 ADC count digital comparator thresholds result in a dead-band

for the comparators of approximately five clock pulses. The high

signal to noise ratio of the signal suggests a reduction of the threshold

is justified. When the threshold is reduced to +/- 32 counts,

dead-band drops to only one clock cycle.

< Previous Next

>